ESMT AD62550A

# Class-D Audio Power Amplifier with USB / I2S Interface

#### **Features**

- Compliant with USB Specification v1.1, and USB 2.0 full speed

- Embedded high efficiency, high performance class

D stereo amplifier

- Support I<sup>2</sup>S input and I<sup>2</sup>S output interface of master mode

Sampling frequencies(Fs): 48kHz

- +6dB enhancement(Theater function)

- Support both bus-powered and self-powered operation

- Supports Win Me//2000/XP/Vista and MacOS

- True plug-and-play application, no driver is required for basic USB speaker application

- Support volume/mute control with external button

- Built-in 5V to 3.3V regulator for internal device operation

- Total efficiency 80% for 8Ω load @ -1dB 1kHz sine wave input

- Loudspeaker PSNR & DR (A-weighting)

80dB (PSNR), 78dB (DR) with Bead filter

82dB (PSNR), 78dB (DR) with Chock filter

- Anti-pop design

- Over-temperature protection

- Under-voltage shutdown

- Short-circuit detection

- 12 MHz Crystal Input

- 32-pin LQFP(Pb free)

### **Description**

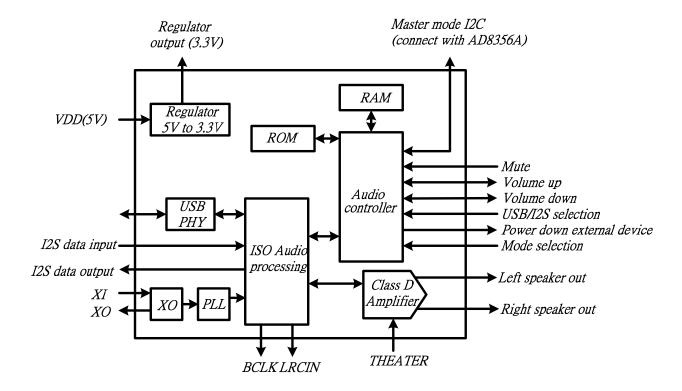

AD62550A is a single chip of Class-D audio amplifier with USB/I<sup>2</sup>S interface. When using the power supplied from the USB port, AD62550A can drive a pair of up to 1W speakers due to the built-in, high efficiency and high performance class D amplifiers. The device also has an I<sup>2</sup>S input port and I<sup>2</sup>S output port. The I<sup>2</sup>S input port allows other external audio sources to use the class D amplifier to share the speakers. The I<sup>2</sup>S output port allows other high performance audio device (i.e. AD8356A/AD8256A) to be controlled by AD62550A.

### **Functional Block Diagram**

Elite Semiconductor Memory Technology Inc. / Elite MicroPower Inc. Publication Date: Sep. 2011 Revision: 1.7 1/16

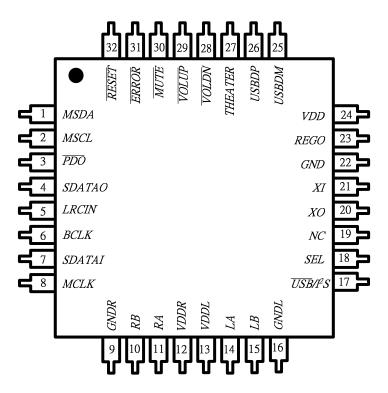

## **Pin Assignment**

# **Pin Description**

| Pin | Name   | Туре | Description                           | Characteristics                  |

|-----|--------|------|---------------------------------------|----------------------------------|

| 1   | MSDA   | I/O  | I <sup>2</sup> C's SDA of Master mode | Schmitt trigger TTL input buffer |

| 2   | MSCL   | 0    | I <sup>2</sup> C's SCL of master mode |                                  |

| 3   | PDO    | 0    | Power-down output (Note1)             |                                  |

| 4   | SDATAO | 0    | Serial audio output (Note1)           |                                  |

| 5   | LRCIN  | 0    | L/R clock output(Fs) (Note1)          |                                  |

| 6   | BCLK   | 0    | BCLK output(64xFs) (Note1)            |                                  |

| 7   | SDATAI | I    | Serial audio data input               | Schmitt trigger TTL input buffer |

| 8   | MCLK   | 0    | Master clock(256xFs)                  |                                  |

| 9   | GNDR   | Р    | Ground for right channel              |                                  |

| 10  | RB     | 0    | Right channel output-                 |                                  |

| 11  | RA     | 0    | Right channel output+                 |                                  |

| 12  | VDDR   | Р    | Supply for right channel              |                                  |

| 13  | VDDL   | Р    | Supply for left channel               |                                  |

| 14  | LA     | 0    | Left channel output+                  |                                  |

| 15  | LB     | О    | Left channel output-                  |                                  |

| 16  | GNDL   | Р    | Ground for left channel               |                                  |

Elite Semiconductor Memory Technology Inc. / Elite MicroPower Inc. Publication Date: Sep. 2011

Revision: 1.7 2/16

| 17 | USB/I <sup>2</sup> S | I   | Low is USB mode, high is I <sup>2</sup> S mode             | Schmitt trigger TTL input buffer |

|----|----------------------|-----|------------------------------------------------------------|----------------------------------|

| 18 | SEL                  | I   | Mode selection bit                                         | Schmitt trigger TTL input buffer |

| 19 | NC                   | NC  | No connection                                              |                                  |

| 20 | XO                   | 0   | Crystal output                                             |                                  |

| 21 | XI                   | I   | Crystal input                                              |                                  |

| 22 | GND                  | Р   | Ground                                                     |                                  |

| 23 | REGO                 | 0   | 3.3V regulator output                                      |                                  |

| 24 | VDD                  | Р   | 5V supply voltage                                          |                                  |

| 25 | USBDM                | I/O | USB data D-                                                |                                  |

| 26 | USBDP                | I/O | USB data D+                                                |                                  |

| 27 | THEATER              | I   | Theater mode, high active                                  | Schmitt trigger TTL input buffer |

| 28 | VOLDN                | I   | Volume down, low active                                    | With internal pull-up resistor   |

| 29 | VOLUP                | I   | Volume up, low active                                      | With internal pull-up resistor   |

| 30 | MUTE                 | I   | I Power-down and mute of Class D Schmitt trigger TTL input |                                  |

| 31 | ERROR                | 0   | Error output Open-Drain output                             |                                  |

| 32 | RESET                | I   | Reset signal                                               | Schmitt trigger TTL input buffer |

Note1: Must be strapped resistor  $1M\Omega$  to 3.3V(REGO) or GND. BCLK, LRCIN and PDO must be strapped to GND. SDATAO is strapped to GND by  $1M\Omega$  when AD62550A's volume/mute is controlled by external button, otherwise strapped to 3.3V when AD62550A is  $I^2C$  slave mode for SEL1 is logic LOW.

### **Ordering Information**

| Product ID  | Package | Packing                                | Comments |

|-------------|---------|----------------------------------------|----------|

| AD62550A-LG | LQFP-32 | 250 Units/ Tray<br>10 Trays/ Small Box | Green    |

### **Marking Information**

#### AD62550A

Marking Information

Line 1: LOGO

Line 2 : Product No Line 3 : Tracking Code Line 4 : Date Code

Elite Semiconductor Memory Technology Inc. / Elite MicroPower Inc. Publication Date: Sep. 2011

Revision: 1.7 3/16

# **Absolute Maximum Ratings**

| Symbol           | Parameter                                                        | Parameter Min Max |     | Units |

|------------------|------------------------------------------------------------------|-------------------|-----|-------|

| VDD              | Supply for regulator input (USB power)                           | er) 0 5.5         |     | V     |

| VDDL(R)          | Supply for Left (Right) Channel (USB power)                      | 0 5.5             |     | V     |

| Vi               | Input Voltage                                                    |                   |     | V     |

| T <sub>stg</sub> | Storage Temperature                                              | -65 150           |     | °C    |

| T <sub>a</sub>   | Ambient Operating Temperature                                    | 0                 | 70  | °C    |

|                  | Voltage Difference between V <sub>DDL</sub> and V <sub>DDR</sub> | -1                | 1   | V     |

|                  | V <sub>DDL</sub> (V <sub>DDR</sub> ) Power-on Voltage Ramp       |                   | 0.2 | V/μs  |

# **Recommended Operating Conditions**

| Symbol  | Parameter                     | Тур     | Units |

|---------|-------------------------------|---------|-------|

| VDD     | Supply for regulator input    | 4.5~5.5 | V     |

| VDDL(R) | Supply for Driver Stage       | 3.0~5.0 | V     |

| Ta      | Ambient Operating Temperature | 0~70    | °C    |

# **Digital Characteristics**

| Symbol          | Parameter                 | Min | Тур | Max | Units |

|-----------------|---------------------------|-----|-----|-----|-------|

| $V_{IH}$        | High-Level Input Voltage  | 2.0 |     |     | V     |

| V <sub>IL</sub> | Low-Level Input Voltage   |     |     | 0.8 | V     |

| V <sub>OH</sub> | High-Level Output Voltage | 2.4 |     |     | V     |

| V <sub>OL</sub> | Low-Level Output Voltage  |     |     | 0.4 | V     |

| Cı              | Input Capacitance         |     | 6.4 |     | pF    |

### **General Electrical Characteristics**

| SYMBOL           | PARAMETER                                         | CONDITION         | MIN        | TYP        | MAX        | UNITS |

|------------------|---------------------------------------------------|-------------------|------------|------------|------------|-------|

| I <sub>USB</sub> | USB Controller Operation Current                  | VDD=5V            |            | 44         |            | mA    |

| IPD              | Supply Current during suspend mode                |                   |            | 410        | 450        | uA    |

|                  | Regulator Current Limit (for REGO)                | 4.5V≦VDD<br>≦5.5V |            |            | 90         | mA    |

|                  | Junction Temperature for Driver<br>Shutdown       | ≥0.50             |            | 150        |            | °C    |

|                  | Temperature Hysteresis for Recovery from Shutdown |                   |            | 20         |            | °C    |

| UVH              | Under Voltage Disabled (for REGO)                 |                   |            | 2.8        |            | V     |

| UVL              | Under Voltage Enabled (for REGO)                  |                   |            | 2.7        |            | V     |

| Fsw              | Switching Rate of Loudspeakers                    |                   | 8Fs        | 8Fs        | 8Fs        | Hz    |

| TPWM             | Minimum PWM pulse width                           |                   | 1<br>256Fs | 1<br>256Fs | 1<br>256Fs | Sec   |

| RSC              | Loudspeaker Short-Circuit Detection (Note2)       | VDDR(L)=5V        |            | 2.8        | 3.2        |       |

Note2: Loudspeaker short-circuit protection is effective only when external LC or ferrite bead filters are properly used. Long time short-circuit will reduce device reliability. AD62550A protects itself from short-circuit damage only when the lines connected to speaker are shorted to each other or to GND. AD62550A will be burnt if the lines connected to loudspeaker are shorted to VDDL(VDDR).

### **Package Options**

| Package Type | Part Number | Thermal Information                           |

|--------------|-------------|-----------------------------------------------|

| LQFP-32      | AD62550A    | $\theta_{\text{JA}} = 59.9^{\circ}\text{C/W}$ |

### **Electrical Characteristics and Specifications for Loudspeaker**

Condition: VDD=VDDL=VDDR=5V, F<sub>S</sub>=48kHz, Load=8Ω with Bead filter. Input is 1kHz sinewave.

| Symbol            | Parameter                          | Condition            | Input Level | Min | Тур  | Max | Units |

|-------------------|------------------------------------|----------------------|-------------|-----|------|-----|-------|

| P <sub>OMAX</sub> | Maximum RMS Output Power / Ch      |                      | 0dB         |     | 2    |     | W     |

| D                 | RMS Output Power for Each Channel  | 10% THD+N            | -4.2dB      |     | 1.58 |     | W     |

| P <sub>OMAX</sub> | Kins Output Fower for Each Charmer | 1% THD+N             | -6.0dB      |     | 1.2  |     | W     |

| I <sub>cc</sub>   | Required RMS Supply Current        |                      | -7dB        |     | 0.66 |     | Α     |

| THD+N             | Total Harmonic Distortion+Noise    |                      | -7dB        |     | 0.54 |     | %     |

| SNR               | Signal to Noise Ratio (Note3)      |                      | -7dB        |     | 78   |     | dB    |

| DR                | Dynamic Range (Note3) (Note4)      |                      | -66dB       |     | 78   |     | dB    |

| PSRR              | Power Supply Rejection Ratio       |                      | -66dB       |     | 60   |     | dB    |

|                   | Channel Separation                 |                      | -7dB        |     | 82   |     | dB    |

| η                 | Efficiency                         | P <sub>O</sub> =2.0W | 0dB         |     | 80   |     | %     |

Condition: VDD=VDDL=VDDR=5V, F<sub>S</sub>=48kHz, Load=8Ω with passive LC lowpass filter (L=22μH, C=470nF); Input is 1kHz sinewave.

| Symbol            | Parameter                         | Condition            | Input Level | Min | Тур  | Max | Units |

|-------------------|-----------------------------------|----------------------|-------------|-----|------|-----|-------|

| P <sub>OMAX</sub> | Maximum RMS Output Power / Ch     |                      | 0dB         |     | 2    |     | W     |

| В                 | BMS Output Dower for Each Channel | 10% THD+N            | -4.4dB      |     | 1.6  |     | W     |

| P <sub>o</sub>    | RMS Output Power for Each Channel | 1% THD+N             | -8.4dB      |     | 8.0  |     | W     |

| I <sub>cc</sub>   | Required RMS Supply Current       |                      | -7dB        |     | 0.55 |     | Α     |

| THD+N             | Total Harmonic Distortion+Noise   |                      | -7dB        |     | 1.45 |     | %     |

| SNR               | Signal to Noise Ratio (Note3)     |                      | -7dB        |     | 80   |     | dB    |

| DR                | Dynamic Range (Note3) (Note4)     |                      | -66dB       |     | 82   |     | dB    |

| PSRR              | Power Supply Rejection Ratio      |                      | -66dB       |     | 60   |     | dB    |

|                   | Channel Separation                |                      | -7dB        |     | 82   |     | dB    |

| η                 | Efficiency                        | P <sub>O</sub> =2.0W | 0dB         |     | 82.7 |     | %     |

Note3: Measured with A-weighting filter.

Note4: Dynamic Range (DR) is defined as Signal to Noise Ratio (SNR) at the highest volume level plus 60dB. In brief, DR= SNR of the highest volume level + 60dB.

Elite Semiconductor Memory Technology Inc. / Elite MicroPower Inc. Publication Date: Sep. 2011

Revision: 1.7 6/16

### **Electrical Characteristics and Specifications for Loudspeaker**

• Condition: VDD=VDDL=VDDR=5V,  $F_S$ =48kHz, Load=4 $\Omega$  with Bead filter. Input is 1kHz sinewave.

| Symbol            | Parameter                             | Condition            | Input Level | Min | Тур  | Max | Units |

|-------------------|---------------------------------------|----------------------|-------------|-----|------|-----|-------|

| P <sub>OMAX</sub> | Maximum RMS Output Power / Ch         |                      | 0dB         |     | 3.5  |     | W     |

| Po                | RMS Output Power for Each Channel     | 10% THD+N            | -4.3dB      |     | 2.6  |     | W     |

| Го                | Rivis Output Fower for Each Charliner | 1% THD+N             | -7.9dB      |     | 1.43 |     | W     |

| I <sub>cc</sub>   | Required RMS Supply Current           |                      | -7dB        |     | 1.11 |     | Α     |

| THD+N             | Total Harmonic Distortion+Noise       |                      | -7dB        |     | 1.12 |     | %     |

| SNR               | Signal to Noise Ratio (Note3)         |                      | -7dB        |     | 78   |     | dB    |

| DR                | Dynamic Range (Note3) (Note4)         |                      | -66dB       |     | 75   |     | dB    |

| PSRR              | Power Supply Rejection Ratio          |                      | -66dB       |     | 60   |     | dB    |

|                   | Channel Separation                    |                      | -7dB        |     | 82   |     | dB    |

| η                 | Efficiency                            | P <sub>0</sub> =3.5W | 0dB         |     | 78.8 |     | %     |

• Condition: VDD=VDDL=VDDR=5V,  $F_s$ =48kHz, Load=4 $\Omega$  with passive LC lowpass filter (L=10 $\mu$ H, C=470nF); Input is 1kHz sinewave.

| Symbol            | Parameter                             | Condition            | Input Level | Min | Тур  | Max | Units |

|-------------------|---------------------------------------|----------------------|-------------|-----|------|-----|-------|

| P <sub>OMAX</sub> | Maximum RMS Output Power / Ch         |                      | 0dB         |     | 3.5  |     | W     |

| В                 | RMS Output Power for Each Channel     | 10% THD+N            | -4.6dB      |     | 2.67 |     | W     |

| P <sub>o</sub>    | Rivis Output Fower for Each Charliner | 1% THD+N             | -10.5dB     |     | 0.84 |     | W     |

| I <sub>cc</sub>   | Required RMS Supply Current           |                      | -7dB        |     | 0.9  |     | Α     |

| THD+N             | Total Harmonic Distortion+Noise       |                      | -7dB        |     | 2.7  |     | %     |

| SNR               | Signal to Noise Ratio (Note3)         |                      | -7dB        |     | 80   |     | dB    |

| DR                | Dynamic Range (Note3) (Note4)         |                      | -66dB       |     | 82   |     | dB    |

| PSRR              | Power Supply Rejection Ratio          |                      | -66dB       |     | 60   |     | dB    |

|                   | Channel Separation                    |                      | -7dB        |     | 82   |     | dB    |

| η                 | Efficiency                            | P <sub>O</sub> =3.5W | 0dB         |     | 82.6 |     | %     |

Note3: Measured with A-weighting filter.

Note4: Dynamic Range (DR) is defined as Signal to Noise Ratio (SNR) at the highest volume level plus 60dB. In brief, DR= SNR of the highest volume level + 60dB.

Elite Semiconductor Memory Technology Inc. / Elite MicroPower Inc. Publication Date: Sep. 2011

Revision: 1.7 7/16

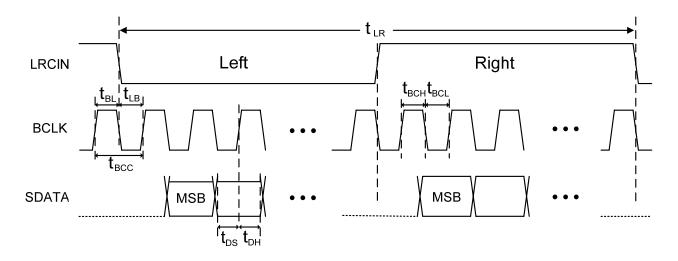

# **Interface Configuration**

I<sup>2</sup>S

| Symbol           | Parameter                         | Min    | Тур | Max   | Units |

|------------------|-----------------------------------|--------|-----|-------|-------|

| $t_{LR}$         | LRCIN Period (1/F <sub>S</sub> )  | 10.41  |     | 125   | μS    |

| t <sub>BL</sub>  | BCLK Rising Edge to LRCIN Edge    | 50     |     |       | ns    |

| t <sub>LB</sub>  | LRCIN Edge to BCLK Rising Edge    | 50     |     |       | ns    |

| t <sub>BCC</sub> | BCLK Period (1/64F <sub>S</sub> ) | 162.76 |     | 1953  | ns    |

| t <sub>BCH</sub> | BCLK Pulse Width High             | 81.38  |     | 976.5 | ns    |

| t <sub>BCL</sub> | BCLK Pulse Width Low              | 81.38  |     | 976.5 | ns    |

| t <sub>DS</sub>  | SDATA Set-Up Time                 | 50     |     |       | ns    |

| t <sub>DH</sub>  | SDATA Hold Time                   | 50     |     |       | ns    |

## **Operation Descriptions**

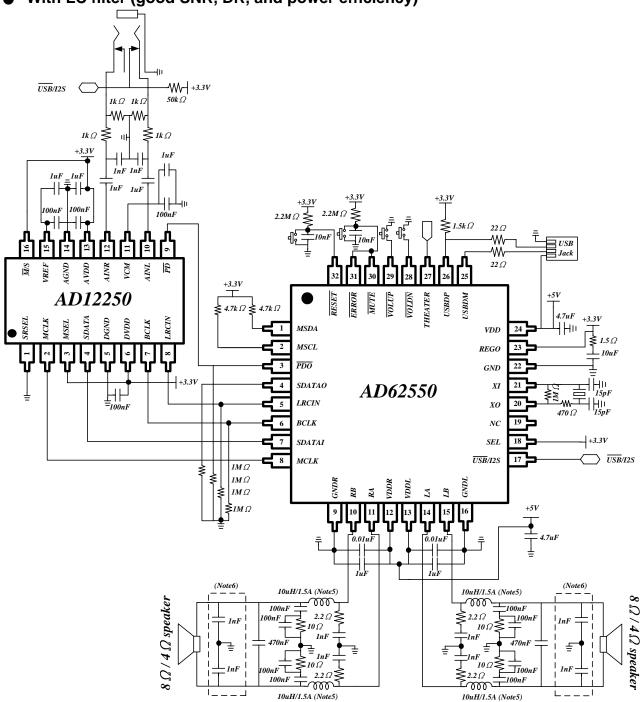

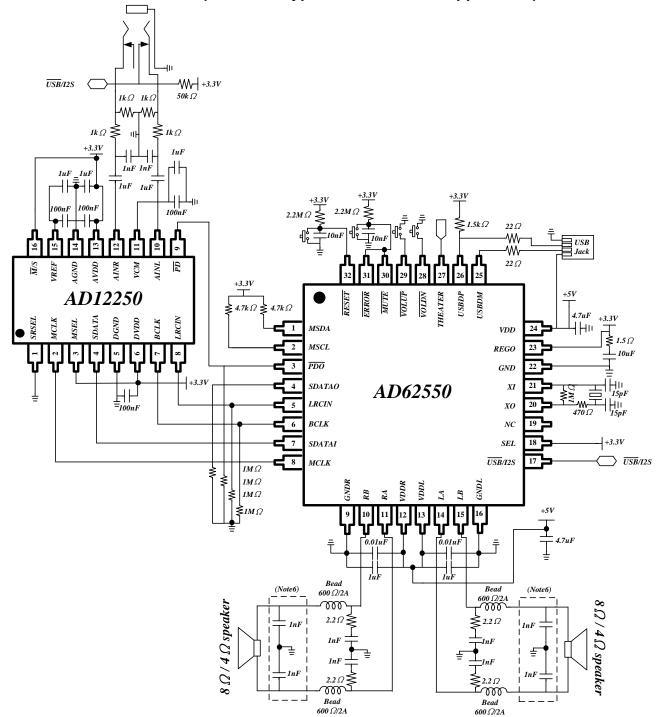

The following figure illustrates two more advanced applications that use AD62550A, together with an external ADC, e.g., AD12250A from ESMT that can convert stereo line-in audio to I<sup>2</sup>S output to send to AD62550A, and/or an external high-end class D amplifier such as AD8356A.

Both applications, a switch is used to select audio stream from either USB port or  $I^2S$  port. When the audio stream is from  $I^2S$  port, the device is operating as "docking station" mode. When the audio stream is from USB port, the device is operating as "USB speaker" mode. When AD8356A is used, since it can deliver 10Wx2 + 20W (subwoofer) power, USB bus power may be insufficient and local power supply is required. Functional description follows.

#### **SEL**

|     | 0                  | 1                  |  |  |

|-----|--------------------|--------------------|--|--|

| SEL | External amplifier | Internal amplifier |  |  |

#### **Volume Control**

Audio volume control is low active. Duration of low level must be longer than 3ms. The highest volume gain is 6dB for THEATER is logic HIGH and 0dB for THEATER is logic LOW, referred to the original input signal level.

#### **RESET**

When RESET is low, AD62550A will clear the data of internal storage elements and set the default volume level of class-D amplifier. The default volume level is –18dB for THEATER is logic HIGH and -24dB for THEATER logic LOW.

#### Mute control

MUTE is low active. Duration of low level must be longer than 3ms.

#### Self-protection circuit (values used here are typical values)

AD62550A has built-in thermal, short-circuit and under-voltage detection circuits. If the internal thermal detection junction temperature is higher than 150°C, the loudspeaker power stages will be turned off. The thermal detection circuit has a temperature hysteretic characteristic such that the AD62550A will return to normal operation when the device is cooled down to about 20°C. Due to the process variation, the triggering temperature values can have around 10% variation.

To protect loudspeaker power stages when the loudspeaker output is shorted each other or shorted to GND, the output loading detection circuits are built-in and proper protection action will take place once the short circuit condition is detected.

For normal operation, the loudspeaker output resistance larger than  $3.4\Omega$  is required. Otherwise, the short-circuit detectors will pull the ERROR pin to low. To effectively protect AD62550A from short-circuit, the ERROR pin and RESET / MUTE pin are suggested to connected together. Once the short-circuit condition is detected, the ERROR pin will be pulled to low and whole chip is reset/mute. The output power stages will be shut off. The recommend R and C value for the RC network connected to the RESET / MUTE pin are 2.2M $\Omega$  and 10nF, respectively. The capacitance should be as close to 10nF as possible. When VDDRL is larger than 3.6V, loudspeaker short-circuit protection is reliable only when LC or ferrite bead filters are properly used.

Once the  $V_{REGO}$  is lower than 2.7V, AD62550A will turn off its loudspeaker power stages and the digital circuit will cease operation. When  $V_{REGO}$  becomes larger than 2.8V, AD62550A will return to normal operation.

#### Anti-pop design

AD62550A is has an anti-pop circuit to suppress the annoying pop sounds during initial power on, power down/up, mute, power off and volume level change.

### Switching between USB Speaker mode and docking station mode

When the USB/I2S pin is low, the input audio stream is from USB port. When this pin is high, the input audio stream is from I<sup>2</sup>S input port.

When operating as USB speaker mode, the volume control is from PC. When the user controls the volume from the local control pins, this volume setting is also uploaded to PC via USB protocol for the Windows operating system to take appropriate action.

#### **Sound Theater Effect Mode**

When THEATER pin is high, Sound Theater Mode is established. In this mode, the audio volume is enhanced by +6dB to simulate the theater effect.

Revision: 1.7 10/16

#### **Power Consideration**

AD62550A can be powered by the USB port directly. However, the maximum current supplied by each USB port is limited 500mA. If the total power requirement of the USB audio subsystem is higher than this, local power supply, e.g., a local AC adaptor will have to be used. If the audio subsystem is attached to an USB hub, which is not locally powered, the maximum power from each USB port is only limited to 100mA, and local power must be supplied.

AD62550A

## I<sup>2</sup>C slave mode when SEL is logic Low

AD62550A can also operate as slave in a system when SDATAO is pulled high with  $1M\Omega$ . When operating as a slave mode, AD8356A/8256A is controlled by an external uP. Functions in PC are all disable.

ESMT AD62550A

### Application Circuit Examples for 8Ω/4Ω loudspeaker

• With LC filter (good SNR, DR, and power efficiency)

Note5: When  $8\Omega$ 's loads are used, the 22uH/0.8A inductors are suggested.

Note6: These capacitors should be placed close to speaker jack as possible, and their values should be determined according to EMI test results.

With 1 ferrite bead filter (economic type, moderate EMI suppression)

Note6: These capacitors should be placed close to speaker jack as possible, and their values should be determined according to EMI test results.

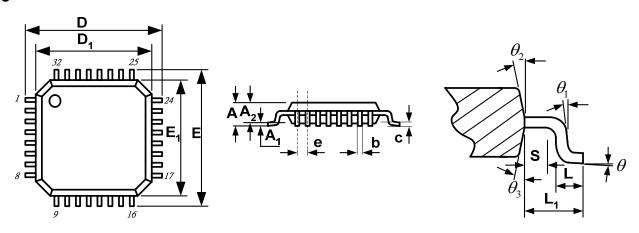

## **Package Dimensions**

• LQFP-32 Package

| Symbol                  | Dimension in mm |      |      | Dimension in inch |       |       |

|-------------------------|-----------------|------|------|-------------------|-------|-------|

| Syllibol                | Min             | Nom  | Max  | Min               | Nom   | Max   |

| А                       | -               | -    | 1.6  | -                 | -     | 0.063 |

| $A_1$                   | 0.05            | -    | 0.15 | 0.002             | -     | 0.006 |

| $A_2$                   | 1.35            | 1.40 | 1.45 | 0.053             | 0.055 | 0.057 |

| b                       | 0.30            | 0.37 | 0.45 | 0.012             | 0.015 | 0.018 |

| С                       | 0.09            | -    | 0.20 | 0.004             | -     | 0.008 |

| θ                       | 0°              | 3.5° | 7°   | 0°                | 3.5°  | 7°    |

| $\theta_1$              | 0°              | -    | -    | 0°                | -     | -     |

| $\boldsymbol{\theta}_2$ | 12° TYP         |      |      | 12° TYP           |       |       |

| $\theta_3$              | 12° TYP         |      |      | 12°TYP            |       |       |

| D                       | 9.00 BSC        |      |      | 0.354 BSC         |       |       |

| D <sub>1</sub>          | 7.00 BSC        |      |      | 0.276 BSC         |       |       |

| E                       | 9.00 BSC        |      |      | 0.354 BSC         |       |       |

| E <sub>1</sub>          | 7.00 BSC        |      |      | 0.276 BSC         |       |       |

| е                       | 0.80 BSC        |      |      | 0.031 BSC         |       |       |

| L                       | 0.45            | 0.60 | 0.75 | 0.018             | 0.024 | 0.030 |

| L <sub>1</sub>          | 1.00 REF        |      |      | 0.039 REF         |       |       |

| S                       | 0.20            | -    | -    | 0.008             | -     | -     |

# **Revision History**

| Revision | Date       | Description                                                                                                                                                                                                                                                                                                                                                |  |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.1      | 2006.08.21 | Original                                                                                                                                                                                                                                                                                                                                                   |  |

| 1.0      | 2006.11.27 | Update measurement data.                                                                                                                                                                                                                                                                                                                                   |  |

| 1.1      | 2006.12.28 | Application circuit updated     Modify pin23 description     Modify output wattage from 10W/20W to 8.7W/16.7W                                                                                                                                                                                                                                              |  |

| 1.2      | 2007.01.12 | Added GND point at common mode filter                                                                                                                                                                                                                                                                                                                      |  |

| 1.3      | 2007.04.27 | <ol> <li>P1, delete 3.3V Operation with 5V tolerate I/O; and added: Sampling frequencies (FS): 48kHz</li> <li>P2-P3, modified pin1 \( \cdot 7 \cdot 17-19 \cdot 27 \cdot 30 \) and 32 characteristics become "Schmitt trigger TTL input buffer"; delete pin21 characteristics description.</li> <li>P3, modified symbol "Vi" maximum is to 3.6V</li> </ol> |  |

| 1.4      | 2008.01.07 | Modified maximum rating VDD \cdot \text{VDDL(R) parameter}                                                                                                                                                                                                                                                                                                 |  |

| 1.5      | 2009.09.11 | Modified oscillator circuit     Added Vista OS support     Added order & marking information                                                                                                                                                                                                                                                               |  |

| 1.6      | 2010.02.26 | Put GND node for application circuit                                                                                                                                                                                                                                                                                                                       |  |

| 1.7      | 2011.09.09 | Revise packing information                                                                                                                                                                                                                                                                                                                                 |  |

### **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.